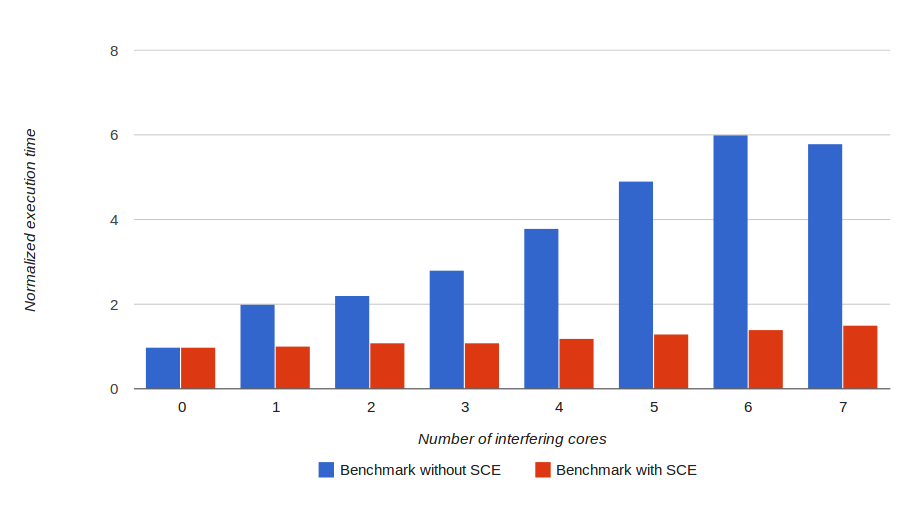

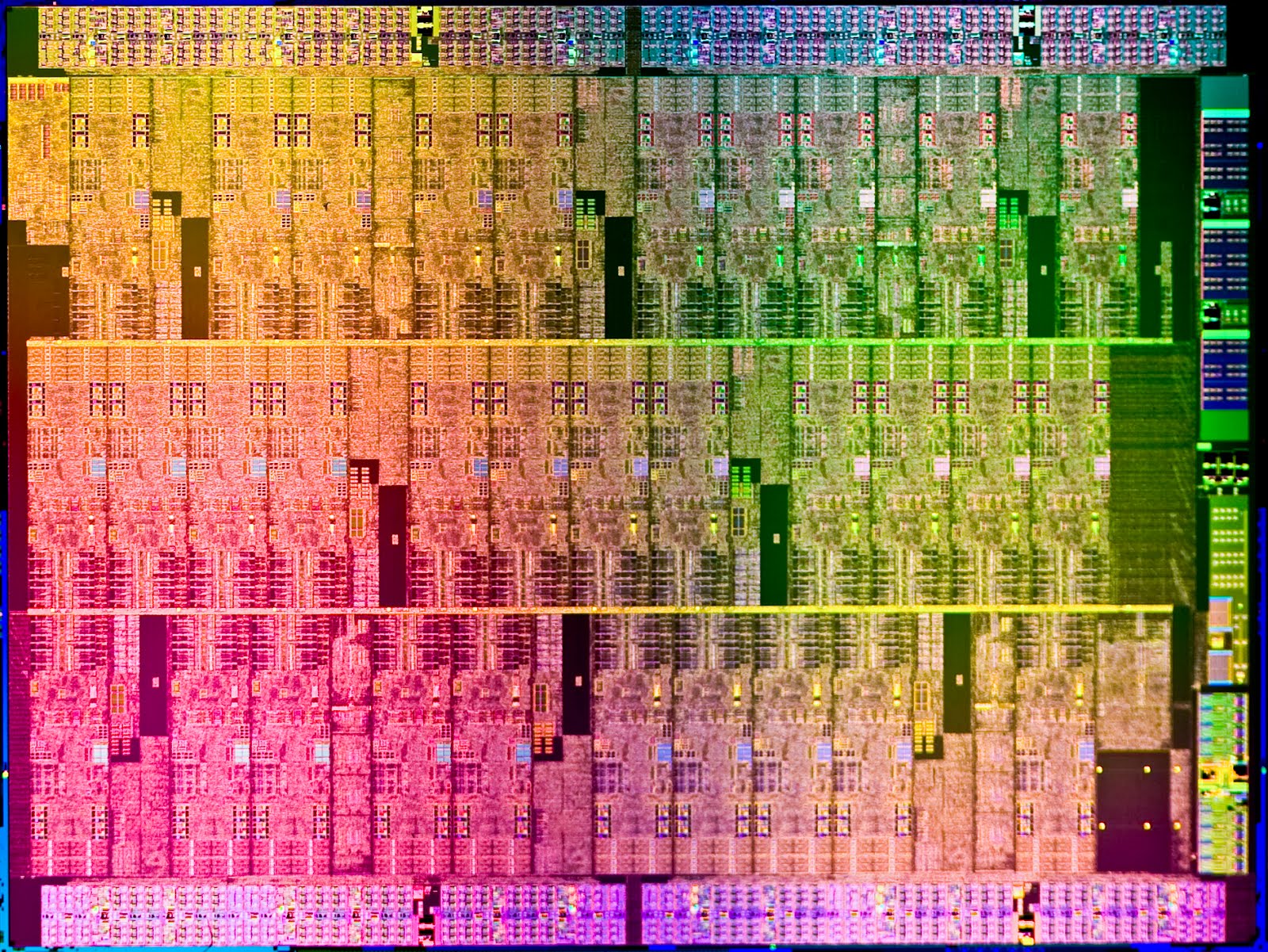

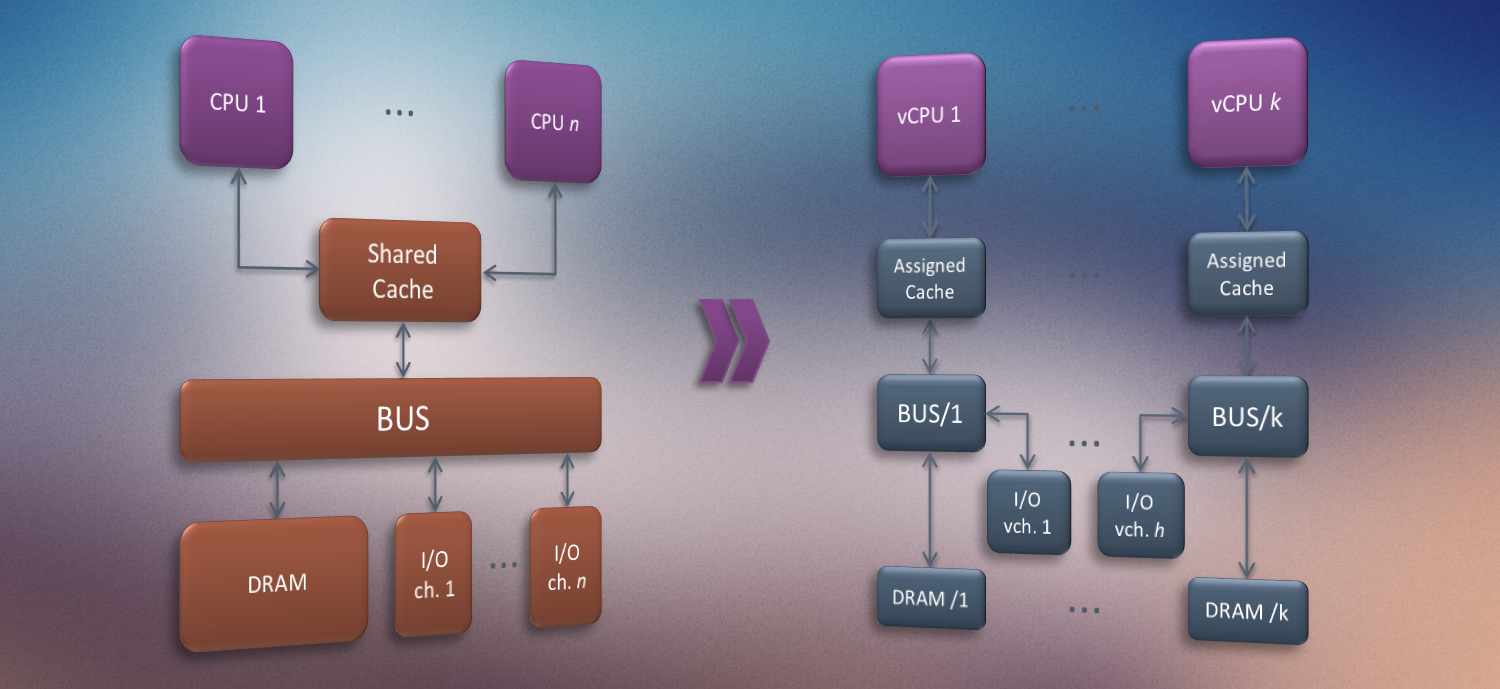

Much of the real time scheduling for single core chips has centered on the CPU, because it has been the bottleneck resource. The emergence of multicore architectures has moved bottleneck resource away from CPU and towards the now globally shared memory banks, memory controllers, last level cache, and I/O channels.

This tutorial presents new technological advancements and solutions to tackle this industry-wide challenge; it introduces the notion of Single Core Equivalent (SCE) software architecture for multicore systems. If managed according to SCE policies, each core can be treated as stand‐alone single-core chip from the point of view of real-time schedulability analysis and certification process. Without a technology like SCE, the change of workload in one core could result in uncontrolled adverse impact on the schedulability of tasks in other cores, triggering the recertification of safety critical applications running in other cores. The time and costs of such recertification is economically unsustainable. This problem is especially critical for the avionic industry. For example, assume that companies A, B, C, D were given IMA partitions in core 1 and their applications were certified. Now, if an application of company E in Core 2 invalidates the schedulability of core 1’s applications, who should do the modification, recertification and pay the bill? Is company E qualified to do the work for companies A, B, C and D? Suppose that Company E pays A, B, C and D to make the changes. What if the modification in Core 1 now invalidates company E’s software schedulability in core 2? Skyrocketing integration costs aside, how can we sort out such circular liability mess?

This tutorial examines the effects of both storage and I/O channel bottlenecks and how to deal with them; it introduces the key theoretical concepts behind SCE and reviews the main implementation aspects faced when trying to implement the SCE architecture framework on modern commercial‐off‐the‐shelf multicore platforms.

National Science Foundation through grant

CNS-1219064 and grant CNS-1302563.